深亚电子,中高端pcb设计、pcb制板、元器件选型、SMT贴装一站式服务

您的位置:

PCB设计中如何根据阻抗计算走线线宽?

- 发布时间:2022-09-07 10:59:46

- 浏览量:1105

分享:

在我们PCB设计中,阻抗线走多款,差分线走多大间距,这些都是需要PCB设计工程师工程师掌握的。

下面我们以4层板为例,来简单介绍一下layout中如何计算阻抗线的线宽

下面来先看下我们叠层吧

板厚1.6MM

TOP……………………………………… 1.8mil(0.5OZ+plating)

FR4……………………………………… 3.8mil(3313)

GND02……………………………………. 1.2mil(1OZ)

CORE……………………………………. 49.4mil

POWER03………………………………….1.2mil(OZ)

FR4…………………………………………3.8mil(3313)

BOTTOM…………………………………..1.8mil(0.5OZ+plating)

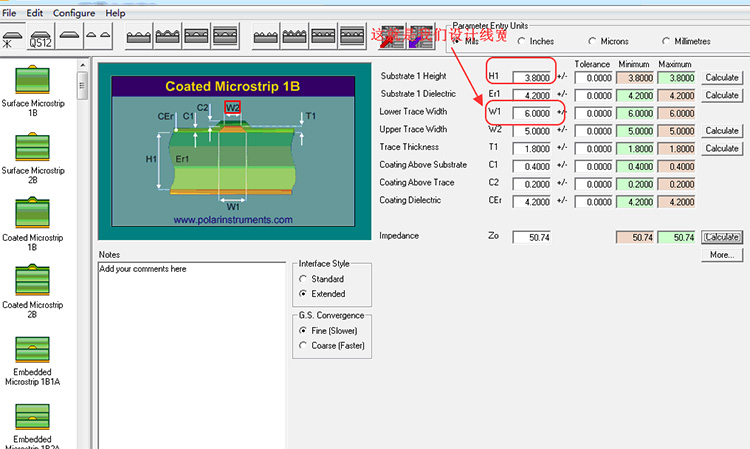

我们计算一下50欧姆阻抗的线宽为例吧

H1:就是我们走线到参考面的距离

ER:介电常数,这里用的4.2,一般普通FR4可以用这个值计算

W1:这个就是我们的设计线宽了

W2:W2是我们线路蚀刻后的上线宽,一般表层,W2比W1小1mil左右

T1:T1是我们的铜厚

C1:绿油厚度

C2:绿油厚度

经过上面的计算,我们50欧姆阻抗线在如上的叠层中的走线线宽为6mil。

THE END

免责声明:部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,意为分享交流传递信息,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者在及时联系本站,我们会尽快和您对接处理。