再建一座新厂,先进封装迎来最强风口!

- 发布时间:2024-06-24 17:04:17

- 浏览量:666

近期业界关于先进封装的动态不断,有关于几家大厂几度扩产先进封装产能的,如日月光、美光、三星、台积电等加码扩产,也有关于先进封装产能不足,如英伟达、AMD、英特尔先进封装产能吃紧,SK海力士、三星、美光2025年HBM产能基本售罄;有争夺先进封装产能的,如台积电先进封装产能被订光,英伟达、AMD一路包到明年等;此外,也有关于先进封装技术创新突破的,如台积电近期晒出最新先进封装技术SoW,三星、SK 海力士推进移动内存堆叠封装技术量产等等。本文将针对行业最新先进封装技术进行科普。

一

最新动态,日月光半导体新建一座先进封装厂

日月光投控旗下日月光半导体6月21日宣布,与日月光旗下宏璟建设在高雄兴建K28厂,预计2026年第四季度完工,重点布局先进封装终端测试以及人工智能(AI)芯片高性能计算。

日月光投控财务经理董宏思表示,K28工厂建设项目由日月光半导体提供持有高雄土地,由宏璟建设提供资金,合建地下1层、地上7层厂房,双方协议合建权利价值分配比例,日月光半导体22.24%,宏璟建设77.76%。兴建完成后,由日月光半导体或子公司取得宏璟建设所属产权的优先承购权。

此前消息显示,日月光高雄厂为应对运营规划,针对先进封装制程的终端测试需求、AI芯片高性能计算及散热需求,购买了大社土地分二期开发。其中,第一期K27厂房已于2023年完工进驻,主要设置Flip Chip及IC测试生产线。

今年2月业绩说明会上,日月光投控表示,为应对先进封装扩充产能,今年整体资本支出将扩大40%至50%,创历史新高。其中65%比重用于封装、尤其是先进封装项目,目前60%多用在封装测试,30%用在电子代工服务。并且日月光投控看好AI发展动能,其预计今年底前AI营收贡献将较去年倍增至5亿美元规模,全年AI相关营收将占ATM(封测)业务总量中个位数,有望高于去年的低个位数,法人预期,明年占比可望挑战高个位数。

先进封装正值鼎盛之际,日月光近两年针对先进封装布局良多。今年2月,英飞凌和日月光投控近日同步公告,日月光投控将投资约21亿元新台币(约合4.79亿元人民币)收购英飞凌位于菲律宾和韩国的两座后段封测厂,扩大在车用和工业自动化应用的电源芯片模块封测与导线架封装,最快今年第2季底完成交易。

今年1月19日,日月光发布公告,马来西亚子公司投资马币6969.6万令吉取得马来西亚槟城州桂花城科技园土地使用权,应对运营需求。产业人士分析,日月光投控此次在马来西亚槟城的投资,主要是为了布局先进封装产能。据悉,日月光半导体已经积极扩展其在马来西亚的封测厂产能,较早之前的2022年11月,槟城新厂四厂及五厂动土,预计于2025年完工。

另外,日月光半导体2023年12月下旬曾公告,承租中国台湾福雷电子位于高雄楠梓厂房,分别为K21的7楼与K22的7楼,扩充封装产能。产业人士分析,日月光半导体将扩充AI芯片先进封装产能。

二

主流先进封装技术介绍

先进封装是指封装集成电路 (IC) 以提高性能的多种创新技术。本质上,就是将传统封装中被延缓的数据传输速度和被损耗的大量功耗,通过技术和结构的创新极大程度的找回。在当前晶体管电路逐渐接近性能极限,摩尔定律放缓,先进制程突破的速度变慢,且难度和成本不断增高的当下,先进封装被业绩寄予厚望。

目前,先进封装主要朝两个方向发展,第一是向上游晶圆制程领域发展(晶圆级封装),直接在晶圆上实施封装工艺,主要技术有Bumping、TSV、Fan-out、Fan-in 等;第二是向下游模组领域发展(系统级封装),将处理器、存储等芯片以及电容、电阻等集成为一颗芯片,压缩模块体积,提升芯片系统整体功能性和灵活性,主要技术包括采用了倒装技术(FC)的系统级封装产品。

本文将重点介绍一下,当前的主流的一些先进封装技术,如晶圆级封装(WLP,Wafer level packaging)、晶圆级扇入扇出型(Fan-out/Fan in)封装、2.5D以及3D IC集成,以及高带宽存储器 (HBM)以及CoWos先进封装、3D 叠动态随机存取存储器 (DRAM) (3DS)、嵌入式硅桥(embedded Si bridges)、TSV硅通孔(Through Silicon Via)、批量回流模制底部填充(MR-MUF:Mass Reflow-Molded Underfill)先进封装等。另外,异构和小芯片中的Chiplet以及混合键合是行业未来重点关注的对象,本讲也将一并叙述。

01

FO封装

FO封装包括三大类:核心扇出型(core fan-out)、高密度扇出型(high-density fan-out)和超高密度FO型(ultra highdensity FO)。核心扇出封装消除了对引线键合或倒装芯片互连的需求,从而提供了改进的 I/O 密度、增强的电气性能和高效的热管理;高密度 (HD) FO 进一步采用了相同的概念,采用先进的重新分布层 (RDL) 和互连结构来实现更高的 I/O 密度;超高密度 (UHD) FO 使用更细间距和更高密度的多层 RDL,以在紧凑封装内提高组件集成度、更大带宽和高级功能。UHD FO 通常应用于较大的封装和多芯片集成,使用 IC 基板来弥合扇出封装和印刷电路板 (PCB) 之间的间隙。

02

晶圆级芯片级封装 (WLCSP)

WLCSP 涉及将 IC 直接封装在晶圆上,从而消除了单独的芯片分割和封装步骤。WLCSP具有紧凑的外形尺寸、增强的电气性能和成本效率,使其成为尺寸、重量和性能至关重要的移动设备和可穿戴设备的理想选择。

03

倒装芯片fcBGA/CSP

这些技术涉及使用焊料微凸块或铜柱将 IC 正面朝下直接安装到有机基板上。与传统引线键合技术相比,倒装芯片 BGA/CSP 解决方案提供更小的占地面积、更短的互连路径、更高的 I/O 密度以及更高的电气性能。这些特性对于服务器、游戏机和网络设备等 HPC 应用尤其重要。

04

2.5D/3D堆叠封装

2.5D/3D 堆叠封装涉及垂直堆叠多个裸片或芯片,形成三维结构。该平台可实现更高的集成度、更高的性能和更小的外形尺寸,使其成为应对人工智能、5G 和 HPC 应用挑战的重要技术。2.5D/3D 堆叠封装中的具体应用包括使用混合键合技术的 CIS、用于更快数据访问和改进内存带宽的 HBM、用于高度集成系统的 3D-SoC 以及用于提高存储密度和容量的 3D NAND。

05

系统级封装 (SiP)

SiP是一种将多个 IC 或“小芯片”集成到单个模块中的 AP 类型。这些小芯片可以包括各种组件,例如处理器、存储器、射频 (RF) 收发器和电源管理 IC 在封装内互连。这种高集成度允许将完整的功能系统包含在单个封装内,使 SiP 成为节省空间的解决方案,非常适合外形尺寸和集成度至关重要的应用,例如移动设备和可穿戴设备。SiP 还在设计和制造方面提供了显着的灵活性,因为每个小芯片都可以使用最适合其功能的工艺技术来制造。

06

EMIB嵌入式硅桥(embedded Si bridges)

将基底技术和硅中介层技术结合起来。它在基板上集成了小的薄层硅桥,用于芯片间的互连,并将桥嵌入封装基板中。如下图所示。EMIB的概念与2.5D封装类似,区别在于没有TSV。通过该封装技术,可以将不同制程的芯片组合在同一芯片封装之中,凸点间距从100um变为55-36um。因此,该技术的特点是良率高,成本低,且无须额外的工艺需求和设计简单。EMIB封装技术就跟台积电的Info封装类似,在功能以及设计上大同小异。

07

TSV硅通孔(Through Silicon Via)

TSV硅通孔(Through Silicon Via)技术是一项高密度封装技术,正在逐渐取代目前比较成熟的引线键合技术。TSV技术通过铜、钨、多晶硅等导电物质的填充,实现硅通孔的垂直电气互连。硅通孔技术可以通过垂直互连减小互联长度,减小信号延迟,降低电容/电感,实现芯片间的低功耗,高速通讯,增加宽带和实现器件集成的小型化。

本段的TSV硅通孔(Through Silicon Via)技术和下文将要叙述的批量回流模制底部填充(MR-MUF:Mass Reflow-Molded Underfill)先进封装技术,均以SK海力士为主宰。

08

批量回流模制底部填充(MR-MUF)先进封装

在先进封装过程中,海力士率先引入MR-MUF回归大规模回流焊工艺,即芯片之间用液态环氧模塑料作为填充材料,导热率比TC-NCF中的非导电薄膜高很多。MR-MUF(Mass Reflow Molded Underfill )是将半导体芯片堆叠后,为了保护芯片和芯片之间的电路,在其空间中注入液体形态的保护材料,并固化的封装工艺技术。与每堆叠一个芯片铺上薄膜型材料的方式对比 工艺效率高,散热方面也更有效。

目前随着HBM芯片堆叠层数的增加,MR-MUF技术容易翘曲、导致晶圆末端弯曲、空洞现象(即保护材料在某些区域分布不均匀)的问题引起行业高度关注。SK海力士方表示,正在推进TSV和MR-MUF的技术发展。与HBM开发初期相比,他们成功地减少了翘曲现象,目前正在开发克服这一问题的技术。下一步,抉择会聚焦在减少空隙。

09

非导电薄膜热压缩TC-NCF

三星在HBM封装上,主要采用的是TC-NCF非导电薄膜热压缩先进封装技术。在每次堆叠芯片时,都会在各层之间放置一层不导电的粘合膜。该薄膜是一种聚合物材料,用于使芯片彼此绝缘并保护连接点免受撞击。随着发展,三星逐渐减少了NCF材料的厚度,将12层第五代HBM3E的厚度降至7微米(μm)。该公司认为这种方法的优点是可以最大限度地减少随着层数增加和芯片厚度减小而可能发生的翘曲,使其更适合构建更高的堆栈。

10

高带宽存储器 (HBM)和CoWos

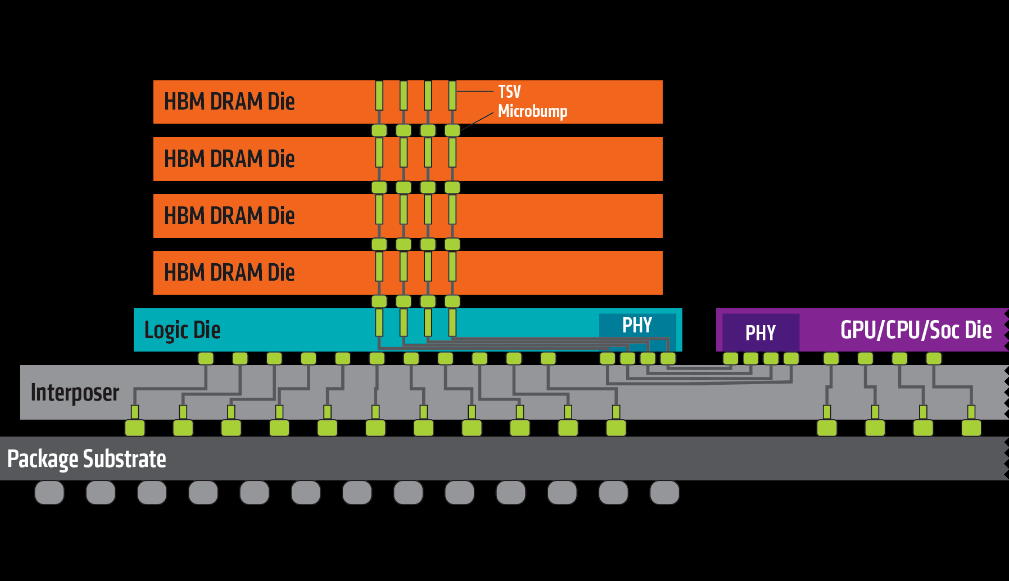

HBM全称High Bandwidth Memory,根本而言,是指基于2.5/3D先进封装技术,把多块DRAM Die像叠罗汉一样堆叠起来的新型存储器。目前,几乎所有的HBM系统都高度绑定了台积电先进封装技术CoWos。

图片来源:AMD

如上图所示,HBM是由多个DRAM堆叠而成,主要利用TSV(硅通孔)和微凸块(Micro bump)将裸片相连接,多层DRAM die再与最下层的Base die连接,然后通过凸块(Bump)与硅中阶层(interposer)互联。同一平面内,HBM与GPU、CPU或ASIC共同铺设在硅中阶层上,再通过CoWoS等2.5D先进封装工艺相互连接,硅中介层通过CuBump连接至封装基板上,最后封装基板再通过锡球与下方PCB基板相连。该产品巧妙的设计大大缩小了尺寸面积,容量扩大的同时,实现了高带宽、低延迟、低功耗的效果。

台积电高级总监表示,目前正在针对HBM4优化CoWoS-L和CoWoS-R技术。CoWoS-L和CoWoS-R都使用超过八层,以实现HBM4的路由超过2000个互连,并具有[适当的]信号完整性。N12FFC+上的HBM4基础芯片将有助于使用TSMC的CoWoS-L或CoWoS-R先进封装技术构建系统级封装(SiP),该技术可提供高达8倍标线尺寸的中介层—足够的空间容纳多达12个HBM4内存堆栈。根据台积电的数据,目前HBM4可以在14mA电流下实现6GT/s的数据传输速率。据台积电表示,该公司目前正与Cadence、Synopsys和Ansys等EDA合作伙伴合作,验证HBM4通道信号完整性、IR/EM和热精度。

11

3D DRAM(3DS)

与传统的内存单元数组与内存逻辑电路分占两侧的2D DRAM存储相比,3D DRAM是一种将存储单元(Cell)堆叠至逻辑单元上方的新型存储方式,从而可以在单位晶圆面积上实现更高的容量。采用3D DRAM结构可以加宽晶体管之间的间隙,减少漏电流和干扰。

在近日举行的Memcon 2024上,三星电子公布了关于3D DRAM开发的细节。三星电子副社长李时宇在会上详细介绍了4F2 Square VCT DRAM及3D DRAM的研发进展。据悉,4F2 Square VCT DRAM是一种基于VCT(垂直沟道晶体管)技术的紧凑型DRAM设计。其通过垂直堆叠技术,将DRAM单元尺寸比现有的6F2 Square DRAM减少约30%,在提高能效的同时大幅降低了单元面积。三星指出,4F2 Square VCT DRAM的开发需要极高的制造精度和更优质的生产材料,还需要解决新材料的应用问题,如氧化沟道材料和铁电体的研发。据悉,三星电子计划在2025年内部发布4F2 Square工艺,并逐步推进3D DRAM的研发,预计在2030年之前推出市场。

12

台积电最新先进封装技术SoW

在近期的北美技术研讨会上,台积电推出了下一代晶圆系统平台——CoW-SoW——该平台将实现与晶圆级设计的3D集成。该技术建立在台积电2020年推出的InFO_SoW晶圆级系统集成技术的基础上。到目前为止,只有特斯拉在其Dojo超级计算机中采用了这项技术,台积电表示该计算机现已投入生产。

在即将推出的CoW-SoW平台中,台积电将在其晶圆系统平台中合并两种封装方法——InFO_SoW和集成芯片系统(SoIC)。通过使用晶圆上芯片(CoW)技术,该方法将能够将存储器或逻辑直接堆叠在晶圆上系统之上。据了解,台积电的CoW-SoW专注于将晶圆级处理器与HBM4内存集成。这些下一代内存堆栈将采用2048位接口,这使得将HBM4直接集成在逻辑芯片顶部成为可能。同时,在晶圆级处理器上堆叠额外的逻辑以优化成本也可能是有意义的。新的CoW_SoW技术预计将在2027年实现大规模生产,但实际产品何时上市还有待观察。

然而,行业消息显示,InFO_SoW技术也有着一定的局限性。例如,使用这种方法制造的晶圆级处理器完全依赖于片上存储器,这可能无法满足未来人工智能的需求(但目前来说很好)。CoW-SoW将解决这个问题,因为它将允许将HBM4放置在此类晶圆上。此外,InFO_SoW晶圆采用单节点加工,该节点不支持3D堆叠,而CoW-SoW产品将支持3D堆叠。

13

异构和小芯片中的Chiplet和混合键合

行业消息显示,在当下先进的封装市场中,异构和小芯片代表了半导体设计和封装的范式转变。异构概念涉及结合不同的材料、工艺和设备来创建一个统一的系统。这种方法可以将多种功能小芯片无缝集成在单个封装上,从而释放半导体设计和制造的新可能性。其中,Chiplet和混合键合成为行业焦点。

Chiplet

据悉,Chiplet是异构的一个基本方面。行业人士表示,小芯片方法代表了一种新兴的半导体设计理念,它将两个或多个分立芯片组合在分解的 SiP 设计中。与可能的单片替代方案相比,小芯片提供了更大的设计灵活性、更快的上市时间、更高的良率和经济效益。小芯片的功能涵盖典型处理器 SoC 中的基本知识产权 (IP) 块,包括中央处理单元 (CPU)、图形处理单元 (GPU)、神经处理单元 (NPU)、I/O 和内存控制器以及接口、高速缓存存储器和模拟功能(SerDes、PLL、DAC、ADC、PHY 等)。

目前Chiplet已成为算力芯片的主流方案,AMD、Intel等半导体巨头共同成立了UCIe产业联盟,NvdiaA100/H100、AMD MI300等主流产品均采用了Chiplet方案,国内算力芯片厂商亦在快速跟进。

混合键合

混合键合则是一项新技术,可以实现半导体器件的垂直堆叠,从而可显著提高器件的性能、功能和可靠性。它是异构的关键推动者,可在键合过程中提供卓越的精度和可靠性。混合键合可确保小芯片之间牢固可靠的连接,从而增强它们在先进封装平台中的集成。这项技术开启了半导体设计的新可能性,使得开发曾经被认为不可能的尖端解决方案成为可能。

混合键合是一项尖端技术,可实现多种芯片架构,满足 HPC、人工智能、服务器和数据中心等高端应用的需求。随着该技术的成熟,受益于高性能芯片间连接,预计将进一步扩展到消费类应用、存储设备以及移动和汽车应用。异构的概念正在推动封装技术的创新,以满足特定的性能、尺寸、功耗和成本要求。混合键合成为高端异构应用的可行途径,将微小的铜焊盘嵌入电介质中,形成电介质到电介质和金属到金属的键合。这种接合技术具有许多优点,例如显着增加的 I/O 连接、最小的信号延迟、扩展的带宽、更高的存储密度以及改进的功率和速度效率。

免责声明:部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,意为分享交流传递信息,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者在及时联系本站,我们会尽快和您对接处理。