中国团队存储器研究取得系列进展

- 发布时间:2024-07-22 17:13:12

- 浏览量:643

近日,中国科学院上海微系统与信息技术研究所宋志棠、雷宇研究团队,在三维相变存储器(3D PCM)亚阈值读取电路、高可靠编程电路、模型方面取得了系列进展,成果发表在国际学术期刊IEEE Transactions on Circuits and Systems I: Regular Papers等。

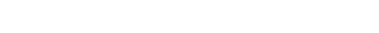

一、3D PCM亚阈值读取电路

3D PCM是最先进的独立式新型存储技术之一。3D PCM读取和编程操作都需要开启双向阈值选通器件(OTS),芯片的疲劳次数被限制在10E6,和传统存储器DRAM的10E16存在差距。CEA-leti(法国原子能委员会)G. Navarro等人于2017年提出了器件层面的亚阈值读取技术,把存储单元读取电压设置在OTS阈值电压以下,提高了芯片寿命(G. Navarro, VLSI’17)。但亚阈值读取技术在电路应用中,有以下困难:(a)读取电流相比常规读取电流下降~100倍,读取速度相应减慢~100倍;(b)读取裕度相比常规读取裕度下降~50倍;(c)漏电与读取电流比上升,可靠性大幅下降。因此,目前亚阈值读取的相关研究仍停留在器件,未跨越到电路层面(J. Woo, ISCAS’19)。

针对以上挑战,团队提出了一种亚阈值自适应参考漏电补偿(ARLC)读出电路。ARLC读出电路有效地采样和补偿了阵列中的泄漏电流,并基于所选单元的数据状态和地址提供自适应参考。结果显示,相比于传统读出电路,ARLC读出电路读取裕度提升11.1倍,读取速度提升85%,良率提升60.3%,读疲劳提升51倍。

图1 亚阈值读取概念和电路

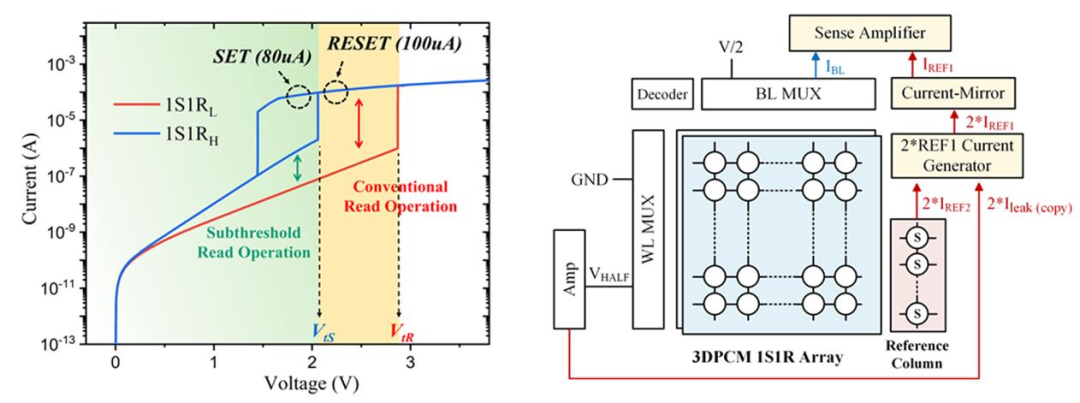

二、高密度3D PCM高可靠编程电路

20 nm工艺节点及以下,3D PCM的写操作可靠性受到写干扰、IR压降、漏电等非理想因素的严重影响,SK Hynix和Micron公司认为这是3D PCM难以微缩的重要原因(Micron @ IEDM’23, SK Hynix @ VLSI’23, IEDM’22 & IEDM’18)。针对以上挑战,团队归纳了影响泄露电流大小的主要因素:选中BL上数据状态、选中单元的行地址和选中单元的列地址。量化了泄露和最优编程电流,提出了地址敏感和数据敏感写电流自动配置电路。其将热干扰导致周围非晶态单元错误的概率降低了900倍以上,单元疲劳提高至原来的7.49倍,显著提高了3D PCM的可靠性。

图2 高密度3D PCM高可靠编程电路

三、1S1R存储单元SPICE模型

1S1R是3D PCM的基本存储单元,带有Monte Carlo功能的 1S1R SPICE 模型是3D PCM可靠性设计和良率提升的关键,也是国际空白。

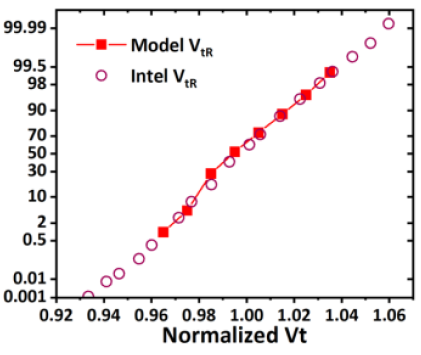

图3 模型和实测数据对比

团队在国际上首次提出带有Monte Carlo功能的1S1R SPICE模型,依据OTS、PCM由电场强度控制阈值转换的特性,引入了参数的统计分布,准确模拟1S1R单元电学特性的统计分布,并在SPICE电路级仿真中还原3D PCM的真实工艺波动,提升了电路设计的可靠性。进一步,使用所提出的模型对亚阈值读取的设计参数进行了探索,包括:亚阈值读取泄漏电流量化、最小读出采样时间设定、最大阵列尺寸设定、减轻泄漏电流影响的方法。

免责声明:部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,意为分享交流传递信息,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者在及时联系本站,我们会尽快和您对接处理。